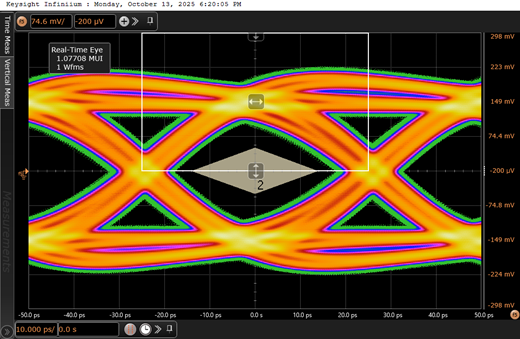

M31 DisplayPort TX IP provides high-performance, multi-lane capability and low power architecture for high-bandwidth applications. DisplayPort TX supports 20Gbps UHBR20, 13.5Gbps UHBR13.5, 10Gbps UHBR10, 8.1Gbps HBR3, 5.4Gbps HBR2, 2.7Gbps HBR and 1.62Gbps RBR data rates. Moreover, the IP supports additional data rate of 6.75/4.32/3.24/2.43/2.16 Gbps per lane for eDP1.4b/1.5a.

- IP Product Lists

- Features

- Supports 1.62G to 20Gbps data rates and compact die area

- Supports X1, X2 and X4 lanes

- Supports post-cursor 1 FFE for Main Link transmitter

- Supports 24/25/26/27 MHz clock input source

- Supports four swing levels for Main Link transmitter

- Supports four pre-emphasis levels for Main Link transmitter

- Supports 20-bit/40-bit (DP1.4) 16-bit/32-bit (DP2.1) databus width of parallel interface

- Supports PLL-alive mode, provide PCLK from PHY

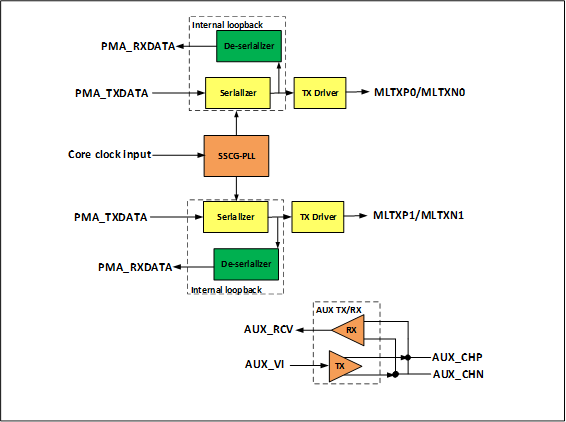

- Supports built-in internal loopback mode for testing

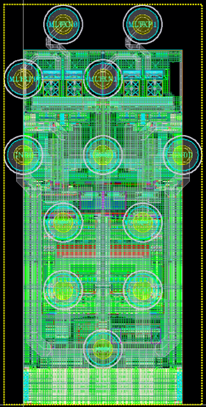

- Supports Wire-Bond (DP1.4) or Flip-Chip (DP2.1) packages

- Available in 28nm, 22nm, 16/12nm, 7/6nm and 5/4nm

- Can be integrated with USB PHY to realize type-C DP alternate at 7nm process